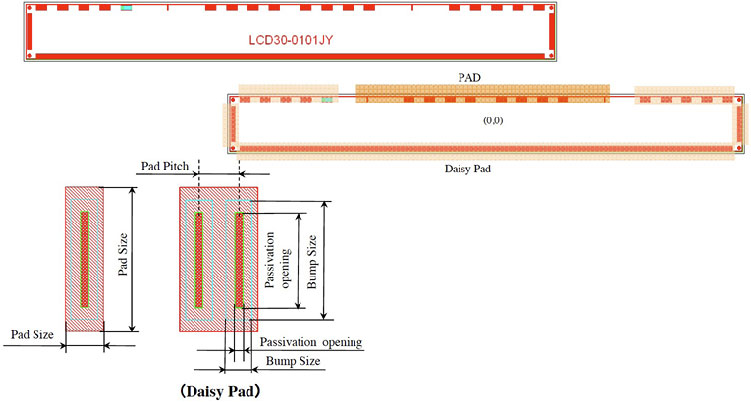

Chip Structure

- Base Layer : P-TEOS*

- Metal Layer : TiW / AI-1.0%Si-0.5%Cu

- Passivation Layer : P-TEOS* / P-SiN

*TEOS : Tetraethoxysilane

| Specifications | |

| Wafer Size | 6 inch |

| Chip Size | 15.1mm×1.6mm |

| Pad pitch | 30μm |

| Function | Daisy Chain |

| Pad config | Peripheral |

| Bump material(process) | Gold(plating) , Cu |

| Pad Size | 28μm×120μm |

| Passivation opening | 6μm×80μm |

| UBM Size | 20μm×100μm |

| Bump Size | 20μm×100μm |

| Scribe width | 100μm |

| Number of Pad | 726 pad/chip |

| Number of Chip | 530 chip/wafer |